**DIGITAL INDUSTRIES SOFTWARE**

### **Intelligent DFM for PCBs**

Design for manufacturing enables fixing errors in a PCB design before it gets built

#### **Executive summary**

Many people think that design for manufacturing (DFM) tools are a fairly recent development. While it is true that the comprehensive software solutions for DFM today are quite advanced, there have always been DFM checks performed on printed circuit boards (PCBs) since they first came into existence. This paper describes how DFM has evolved and why a DFM tool is a "must have" for today and the future of PCB design and manufacturing because it lets you fix problems during design instead of re-designing the board after errors are found by manufacturing.

By Pat McGoff and Kevin Webb

# PCBs: 40 years of evolution, from the physical to the digital

Printed circuit boards have been used to make wiring electronic components easier since the 1950s. Here is a little trivia: What was the first DFM tool used for PCB designs? Answer: The eye loop (Figure 1). Yes, a high-power magnifier, because at that time and for most of the next 40 years, PCBs were designed using colored tape on a Mylar sheet, which was then photographed for board fabrication.

DFM was performed by placing the film on a light table to measure feature sizes, line widths, and spacing using an eye loop with measurement lines etched onto the glass lens. If the film had extraneous features, they would be scraped off with an Xacto knife. Voids would be filled in using a black marker. Simpler times, then. 10 mil lines and spaces. Double-sided PCBs were the norm. Manual DFM was feasible.

Those days are far away now in our rearview mirror. PCBs commonly have 8 to 10 layers to as many as 64 layers. Also reasonably common is the use of build-up technology with laser-formed stacked and staggered microvias, embedded devices – both passive and active – and complex flex and rigid-flex circuits. Fabrication and assembly requirements have

Figure 1. Eye loop used for early DFM.

exceeded what most companies can (or desire) to do in-house, so in many cases, they are outsourced and off-shored.

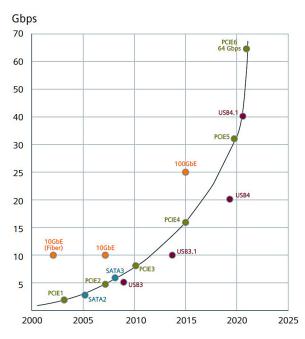

Today's circuits operate at frequencies that only microwave engineers dealt with not long ago (see Figure 2). With those frequencies come new problems: signal integrity, power integrity, crosstalk and unintended radiation. Even stackup designs for multilayer boards must be carefully analyzed to prevent those signal issues.

Figure 2. Electronic circuit operating speeds continue increasing exponentially.

### Today's PCB DFM best practices

As software capabilities increased, DFM tools were conceived to analyze and locate manufacturability issues in PCB designs. Early on, those issues generally related to mechanical constraints such as spacing, line widths and mounting hole locations.

The leading-edge tools now incorporate much more functionality to take new designs to market. DFM has evolved such that it is now an integral part of new product introductions (NPI). Today, NPI software spans design and manufacturing to optimize a PCB for manufacturability. It takes data and knowledge directly from manufacturing that can be used throughout design, fabrication, assembly and test.

Designers employing best practices find that NPI software lets them identify multiple ways to optimize their products during the initial release process, with embedded knowledge of the fabricators' and assembly suppliers' capabilities. It is important to look beyond violations to understanding the challenges and limitations involved in the processes of manufacturing partners, then empowering the product owner to make the trade-off decisions that best serve the company goals.

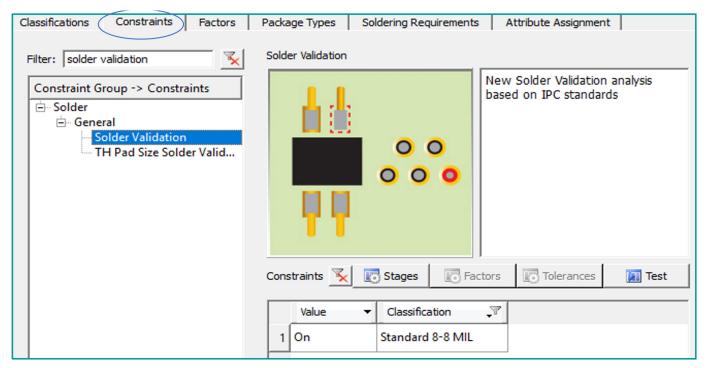

The ideal intelligent DFM approach would comprise a system that coordinated which constraints were applied to a particular board, as shown in the examples in Figure 3. When automated, the software would manage the set of design and process requirements, eliminating confusing configurations and setup requirements.

Similarly, the tool should define the ideal design requirements and limitations of manufacturing processes. This method ensures that a design would be checked to properly assign a correct constraint rule. The constraints would then be used by establishing multiple analysis limits. The results are graphically reported to show the limits of DFM rules based on each of the manufacturers' requirements and what risks exist with the design. The DFM rules engine would automatically consider manufacturing tolerances to ascertain if any DFM violation has occurred. This is possible with the use of intelligent properties embedded in the CAD data. Vias are differentiated from mechanically drilled holes; testpoints are labeled as such and components are attributed by type. If the design data is attributed properly, DFM can be performed in a much more automated, streamlined and correct manner.

The intelligent DFM approach considers the needs of everyone on the team. PCB designers, manufacturing engineers and electronics manufacturing service (EMS) companies or contract manufacturers all benefit from this approach. The PCB designer must meet all internal design and industry guideline requirements with a view of their suppliers' process capabilities. The manufacturing or NPI engineer, generally the technical contact between design and manufacturing, could easily evaluate manufacturing requirements versus multiple processes and suppliers' requirements. In turn, the EMS could evaluate manufacturing requirements compared to their manufac-

turing processes or across multiple locations to ensure a successful manufacturing run.

A side benefit of using intelligent CAD data is that the DFM systems employing algorithms based on CAD feature shapes require just minutes compared to systems based on vector data, which can take hours to run.

|                          | Simple     | Standard   | Complex     | Flex       |

|--------------------------|------------|------------|-------------|------------|

|                          |            |            |             |            |

| Number of Layers         | < 4        | < 12       | < 24        | < 12       |

| Number of Plating Cycles | 1          | 1          | <5          | < 5        |

| Smallest Drill           | <= 8 mils  | <= 5 mils  | <= 4 mils   | <= 5 mils  |

| Maximum Board Thickness  | <= 62 mils | <= 93 mils | <= 115 mils | <= 93 mils |

| IPC Class                | 1          | 2          | 3           | 2          |

| Includes Microvias       | No         | No         | Yes         | No         |

| Rigid-Flex               | No         | No         | No          | Yes        |

Figure 3. Constraints are considered based on the board requirements.

## DFM next practices move beyond "standard" PCB design

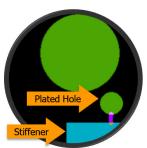

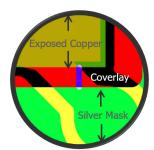

DFM for flexible and rigid-flex circuits has more-or-less been ignored. Because nearly 30 percent of all electronics companies have flex and/or rigid-flex circuits within their product portfolios, it is important to include them in DFM. With the demand for consumer and wearable flexible electronics increasing, flex DFM needs will only continue to accelerate. The materials and manufacturing processes are different for flex and rigid-flex circuits compared to conventional rigid boards, and the DFM tools must support those different needs. Being able to identify features or trace direction changes within a bend area are critical, as is maintaining sufficient clearance around a coverlay zone, for example. Clearly too, an intelligent DFM system must be able to tell the difference between a rigid PCB, a flex-circuit and a rigid-flex circuit. Figure 4 illustrates some of the DFM checks that are unique to rigid-flex designs.

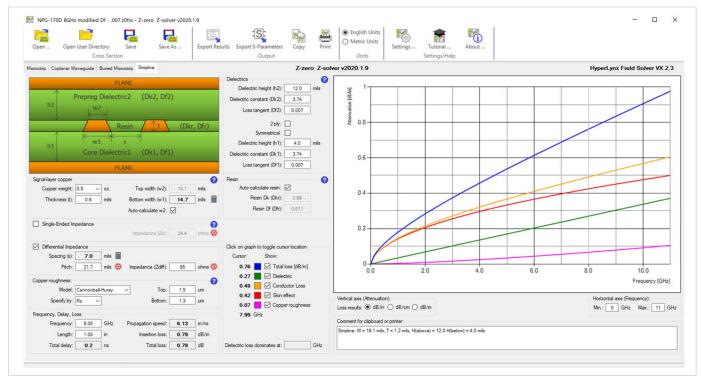

Another area that has not seen the attention it deserves is stackup design. With high-speed boards,

a poorly designed stackup can produce signal integrity problems that may not even be realized until the product is functionally tested – an expensive time to find out. A stackup design tool should not only incorporate signal integrity analysis, but DFM with respect to the stackup as well. The tool should have an extensive library that allows research, comparing and finding the most economical material that meets performance requirements.

Competitive advantage can be increased by running DFM analyses concurrent with the design process. To make this more practical, DFM software ideally must be well-integrated with the PCB design software so that a designer can run the analysis and review the results for DFM within ta familiar environment of layout tools. Someone downstream finding problems after the product is released from design is no longer adequate. Upstream understanding is required to compete today.

Conductors should be perpendicular across the entire bend area

Plated holes too close to a stiffener can lead to cracks in the barrel

Rigid area copper close to interface area can cause copper to crack

Silver mask must remain clear of exposed copper to avoid EMI issues

Figure 4. Rigid-flex circuitry has unique requirements compared to an all-rigid PCB.

## Intelligent DFM for optimizing PCBs automatically

Valor NPI software from Siemens uses expert system logic to automate DFM analysis. High-quality automated DFM analysis is based on a combination of PCB technologies and manufacturing constraints. PCB technology can be automatically determined with intelligent design data. For example, the copper weight of each layer is critical in the fabrication DFM analysis because of the etch compensation applied and, thus, resultant etch-back are going to vary based on the copper weight used.

Copper weight will vary between inner and outer layers. A 3-mil spacing on an inner layer made of 0.5 oz. copper could be acceptable, but more spacing is required on the outer layers – as much as 4-mil spacing based with the use of 1 oz. copper. In addition, sequentially laminated stacked vias require a different set of DFM rules than a conventional, single-lamination PCB.

Letting the DFM software act on each of these constraints automatically saves engineering effort and delivers the desired results consistently for every user, regardless of their manufacturing expertise. In addition, Valor NPI can perform a complete solder analysis, as shown in Figure 5, to locate potential solderability issues.

High-speed stackup design verification becomes much simpler using Siemens Z-planner Enterprise. In the same way Valor NPI uses process and capability data from manufacturers, Z-planner Enterprise uses material properties from the fabricators to run intelligent DFM on the stackup design (Figure 6). With a material library exceeding 150 entries, a designer can select, compare, and run "what if" scenarios to

Figure 5. Valor NPI can run solder validation analyses as part of the DFM checking.

Figure 6. Z-planner Enterprise ensures stackup designs that meet specifications and can be readily manufactured.

optimize material performance versus cost. Plus a wizard lets anyone in the design flow apply expert DFM analysis using actual data from

Certainly the electronics industry has progressed beyond just DFM – Valor NPI software is also used to design and optimize PCB panels. Many companies are inefficient in their panel-design process, even for assembly panels or arrays. Typically, designers will use a 2D mechanical CAD tool to create a drawing of what the assembly panels should look like when received from the bare-board fabricator. Several hours are required to create the drawing and add notes and dimensions, then they send it to their fabricator as a dumb drawing file – "dumb" meaning the drawing file contains no intelligence that the fabricator can key off of in the tooling process. Instead, the fabricator must recreate the panel with their CAM software and send

a proof image back to the designer for approval. Needless to say, with the technology available today, this level of redundant manual processes is unnecessary.

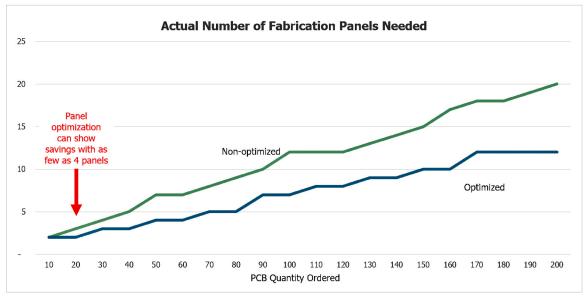

Instead, the design team can easily create assembly panels using the Valor NPI software and include all the elements needed – rails, tooling holes, fiducials and rout or v-score features. Valor NPI can automatically optimize the boards within the assembly panel to minimize the fabrication material costs (Figure 7). When trying to drive down the costs of electronic products, reducing fabrication material costs is often an overlooked opportunity.

We conducted a study with four different customer designs and found panel optimization saved an average of more than \$125,000 annually. Those savings could be realized with just four panels, as shown in the graph in Figure 8. Furthermore, DFM analysis done on the assembly panel can identify

potential manufacturing issues that cannot be identified in the single-up stage. Examples of issues that will be caught by DFM are having a breakaway tab too close to a SMD pad or a device that overhangs the edge of the PCB obstructing machine vision access to a global fiducial.

Figure 7. Valor NPI can optimize both fabrication and assembly panels. Here, fitting the PCBs together in a more efficient pattern of assembly panels produces 20 assembly panels instead of the original design's 12 panels.

Figure 8. Using an actual customer's board design and panels showed optimized panels produced savings with just four panels.

Finally, new product introduction involves creation, validation and delivery of the design data package to the fabrication and assembly houses. Historically, it is delivered as a package comprised of some combination of the following:

- Gerber files

- Drill files

- Netlist files

- Test files

- Manufacturing BOM

- Drill drawings

- Assembly panel drawings

- Route drawings

- · Stackup drawing

- Drawing notes

Oddly, for an industry that drives the digitalization of the planet, PCB production is heavily dependent on manual processes with instructions communicated through 2D, non-relational drawings and documents. Is there anything in documentation that cannot be represented as a data field? Nets that are intentionally shorted? A data field can be tagged to the appropriate nets. Top-side soldermask color?

| Product Summary section -> Attribute   | Value                      | Units |

|----------------------------------------|----------------------------|-------|

| Board Requirements                     |                            |       |

| Board Thickness                        | 0.089200                   | Inch  |

| Additional Requirements                |                            |       |

| Board Outline Tolerance Plus           | 5.000000                   | Mil   |

| Board Outline Tolerance Minus          | 5.000000                   | Mil   |

| Board Thickness Tol Plus               | 3.000000                   | Mil   |

| Board Thickness Tol Minus              | 3.000000                   | Mil   |

| Board Thickness Type                   | over mask on plated copper |       |

| Bottom Legend Color                    | white                      |       |

| Bottom Soldermask Color                | yellow                     |       |

| Flammability Rating Standard           | UL94V-0                    |       |

| General PCB Standard                   | IPC 6012A                  |       |

| Glass Transition Temperature (Tg)      | 110.000000                 |       |

| Legend Sides                           | Both                       |       |

| PCB Acceptability Standard             | IPC 6012A                  |       |

| Peelable Mask Side                     | none                       |       |

| Plated Edge                            | Yes                        |       |

| Plated Slots                           | No                         |       |

| Qualification and Performance Standard |                            |       |

| Soldermask Sides                       | Both                       |       |

| Top Legend Color                       | white                      |       |

| Top Soldermask Color                   | green                      |       |

Figure 9. Data can be transferred from the design to manufacturers completely digitized.

#### Summary

One thing about the electronics industry: it waits for no person and no company. Manual processes affect the ability to compete in a global marketplace. If an electronics producer is not not taking full advantage of DFM tools, they are already behind.

Valor NPI performs DFM analysis concurrent with the design process and is integrated with layout tools, providing the most efficient design-to-manufacturing flow. With today's tools, companies should look at the full release process – DFM, stackup, documentation and communication – to systematically streamline their design to manufacturing process.

#### **Siemens Digital Industries Software**

Americas: 1 800 498 5351

EMEA: 00 800 70002222

Asia-Pacific: 001 800 03061910

For additional numbers, click here.

Siemens Digital Industries Software helps organizations of all sizes digitally transform using software, hardware and services from the Siemens Xcelerator business platform. Siemens' software and the comprehensive digital twin enable companies to optimize their design, engineering and manufacturing processes to turn today's ideas into the sustainable products of the future. From chips to entire systems, from product to process, across all industries, Siemens Digital Industries Software – Accelerating transformation.